�hFPGA�ŗV��ł݂�h�ł́A�Z�~�i�[�p�ɍ쐬�����T���v����H�Ȃǂ����ď����ÂЉ�Ă����܂��B

![]()

![]()

![]() �Z�~�i�J�Â��܂�

�Z�~�i�J�Â��܂�![]()

![]()

![]()

��Ԃ��OK�IIoT�v���O���~���O�����EIoT�J���L�b�gM5StickC Plus2�ō��ʐM�K�W�F�b�g

-- GUI�x�[�X��UIFlow�Ŏn�߂邾��ł��ȒP�v���O���~���O�@

2026�N5��12��(��)CQ�o�ŎЃZ�~�i���[�� CQ�o�ŎЃZ�~�i�E���[��

�ڂ����͂������

![]()

![]()

![]() ZYBO�̖{

ZYBO�̖{![]()

![]()

![]()

FPGA�p�\�R��ZYBO�ō��Linux I/O�~�j�R���s���[�^�@CQ�o�Ł@������

![]()

![]()

![]() Papilio�̖{

Papilio�̖{![]()

![]()

![]()

FPGA��Arduino!!Papilio�ō��f�B�W�^���E�K�W�F�b�g�@CQ�o�Ł@������

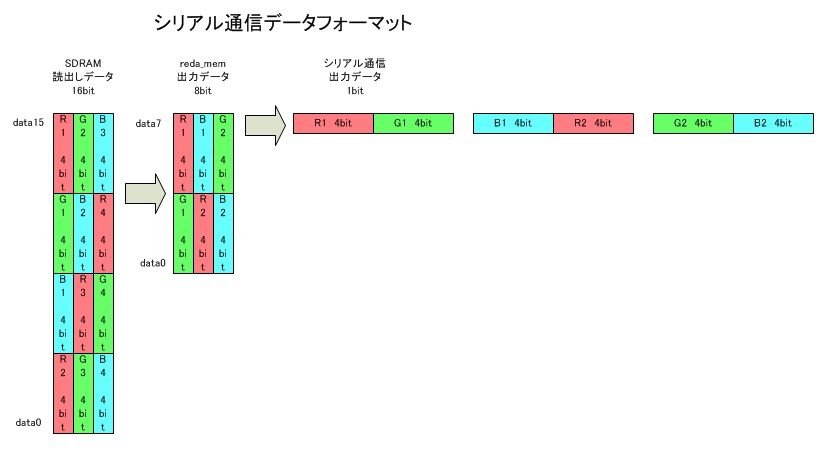

��1�P��@�J�������W���[���̉摜���V���A���ʐM��PC�֓]�����Ă݂�

�@�@����͑�10��̉�H�i�J�������W���[���摜�\���j���x�[�X�ɃV���A���ʐM�iUART�j�o�R��PC�։摜�𑗂��H��lj������̂ŁAPC���v���O�����ƍ��킹�ďЉ�܂��B

�@�摜��FPGA����V���A���ʐM�ŏo�͂���USB-UART�ϊ�����o�R����PC�֓]�����܂��B

�@�܂��AVRAM�̏����݂�Ǐo���ŁA�摜�̓������Y���Ȃ��悤�ɁAVRAM��2�̗̈�ɕ����ēǂݏ������s���悤�ɕύX���Ă��܂��B

�@PC���̃v���O�����̊J���͖������p�ł���Microsoft Visual C++2010 Express���g�p���܂����B

�@�]���@��

�@

�@

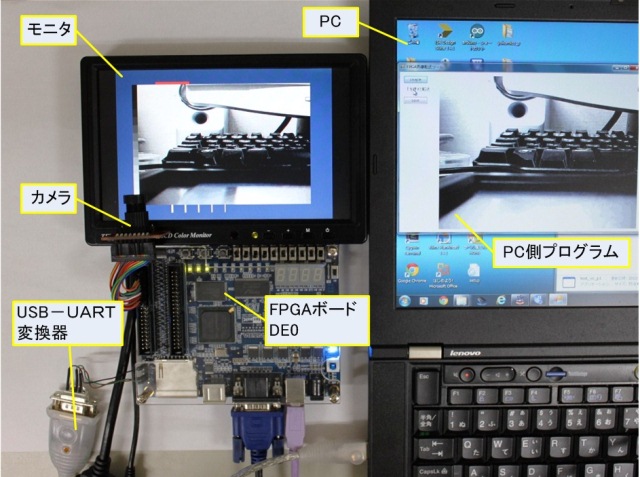

�@���オSVGA���j�^�iRGB�j�A���j�^�̍������J�������W���[���iOV7670�j�A

�@������FPGA�{�[�h�iDE0�j�A����ɂ��̍�����USB-UART�ϊ���A

�@�E���͉摜��]������PC�ł��B

�@ DEO�̃V���A���ʐM�[�q�́ACOM�|�[�g�̒��ڐڑ��ł���d�����x���ŏo�͂���܂��B

�@ �������ADE0��COM�|�[�g�p�R�l�N�^�͂��Ă��Ȃ��̂ŃR�l�N�^��lj�����K�v������܂��B

![]() �J�������W���[���摜PC�]����H�̃\�[�X�izip���k���Ă���܂��j

�J�������W���[���摜PC�]����H�̃\�[�X�izip���k���Ă���܂��j

�@camera_ap_de0_uart_files.zip

�@�@���e

�@�@camera_ap.v�@���Ӊ�H���܂߂�FPGA�̍ŏ�K�w

�@�@read_mem.v�@SDRAM����PC�o�͗p�f�[�^�Ǐo��

�@�@sdram_rd_abt.v�@SDRAM�Ǐo�����N�G�X�g����

�@�@sdram_ctrl.v�@�Ȉ�SDRAM�R���g���[��

�@�@line_buf_in.v�@�����ݗp���C���o�b�t�@

�@�@line_buf_out.v�@�Ǐo���p���C���o�b�t�@

�@�@camera_if.v�@�J�������W���[���C���^�[�t�F�[�X��H

�@�@vram_ctrl.v ���͉摜�̃������ۑ��A�o�͉摜�̃������Ǐo����H

�@�@ov7670_cmd_genv ov76�V�O�̐ݒ���̐���

�@�@i2c_ov7670_ctrl�Dv�@ov76�V�O�̐ݒ���i2c���W���[��������

�@�@svga_if.v SVGA�摜�o�͉�H�i��4��ŏЉ�)

�@�@layer_a.v�@�ړ����锠�̃O���t�B�b�N�����i��4��ŏЉ��j

�@�@layer_b.v�@�J���[�p�^���̃O���t�B�b�N�����i��4��ŏЉ��j

�@�@msg_buf.v�@���b�Z�[�W�o�b�t�@��H(��8��ŏЉ�)

�@�@fifo.v�@���b�Z�[�W�ێ��pFIFO(��8��ŏЉ�)

�@�@ram.v�@���b�Z�[�W�ێ��pFIFO�pRAM(��8��ŏЉ�)

�@�@rs232c_txrx.���@�V���A���ʐM�iRS232C�j�C���^�[�t�F�[�X���W���[��(��R��ŏЉ�)

�@�@camera_ap_test.v camera_ap�̃e�X�g�x���`

�@�@c��mera_ap.qsf�@FPGA�{�[�h��DE0���g�p�����ꍇ��PIN�z�u�w��

�@�@camera_ap.mif�@OV7670�ݒ�p��ROM�f�[�^�t�@�C��

�@�@vcpp_program/test_vc_p1.exe PC���摜�]���v���O����

�@�@vcpp_program/test_vc_p1_src.txt �@PC���摜�]���v���O�����̃\�[�X�R�[�h�̈ꕔ

�@

�@��camera_ap.v���g�b�v��H����Quartus�U�̃v���W�F�N�g���쐬���Ă�������

�@��test_vc_p1_src.txt �̓\�[�X�̈ꕔ�ł��BVC++�̃v���O���������ꍇ�̎Q�l�ɂ��Ă�������

�@���S�Ẵt�@�C�����X�V����Ă��܂��̂ŁA���̃y�[�W���k�f�[�^�ɓ����Ă���vrilog�\�[�X���g�p���Ă�������

�@�����̉�H���g�p����ꍇ�́A���ȐӔC�ł��肢���܂��B

![]() FPGA�ł̓������e

FPGA�ł̓������e

�@![]() FPGA�g�b�v���W���[���icamera_ap.v�j

FPGA�g�b�v���W���[���icamera_ap.v�j

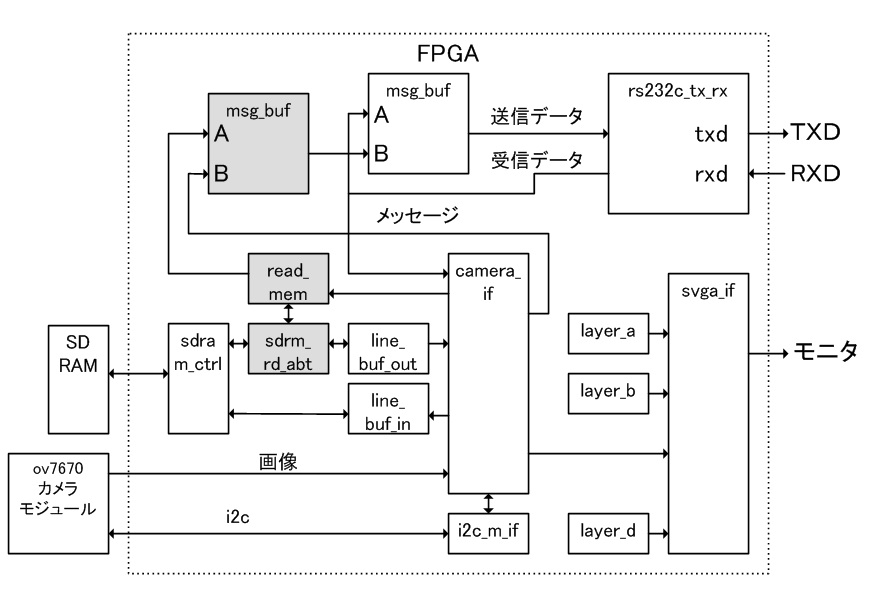

�@�@��10��̉�H��read_mem,sdram_abt,msg_buf��lj����Ă��܂��B���̃��W���[�����ύX�������Ă��܂��B��{����͑�10��A��9��i���̂P,����2�j���Q�Ƃ��Ă��������B

�@�@�lj��̋@�\�͈ȉ���2�_�ł��B

�@�@�P�DVRAM�̏����ݓǏo���ʼn摜�Y���h�~

�@�@��10��܂ł́AVRAM��1��ʂ��������Ă��Ȃ������̂ŁA�����݂ƓǏo���ʼn摜�̃Y���������Ă��܂����B�����VRAM��

�@�@2��ʕ��̗̈���g���A�����݂ƓǏo���œ����̈�ɃA�N�Z�X���Ȃ��悤�ɂ��ĉ�ʂ̃Y����h�~���܂����B

�@�@2�D�摜�]���@�\

�@�@�V���A���ʐM��'M'+CR+LF����M����ƁA���̎��_�œǏo���Ɏg���Ă���VRAM�̈���f�[�^���V���A���ʐM�œ]�����܂��B

�@�@���j�^�\���p�̓Ǎ��݂ƃV���A���ʐM�p�̓Ǎ��݂���������̂�sdram_rd_abt�ŃA�N�Z�X�̒�������Ă��܂��B

�@�@�ȉ��̓u���b�N�}�ł��B�O���[�̃��W���[��������lj��������W���[���ł��B

![]() FPGA�lj��@�\�̓���ڍ�

FPGA�lj��@�\�̓���ڍ�

�@![]() VRAM�̏����ݓǏo���ʼn摜�Y���h�~

VRAM�̏����ݓǏo���ʼn摜�Y���h�~

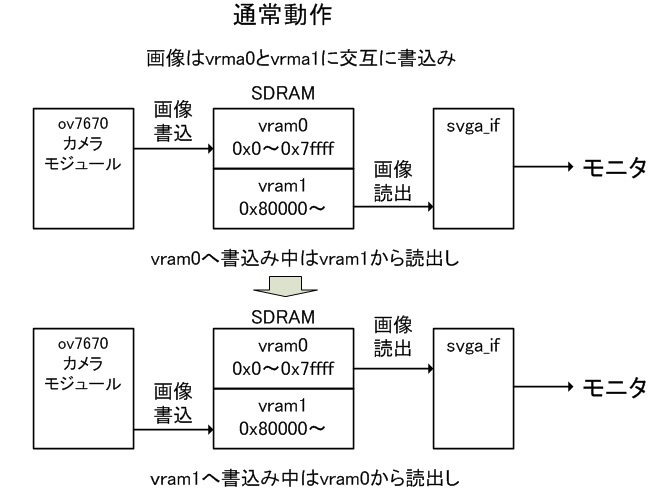

�@�@�V���A���ʐM�ɂ��摜�]�����s���ĂȂ��ʏ��Ԃł́A�J�������W���[������̃f�[�^��vram0�̈��vram1�̈�Ɍ��݂ɏ����݂��s���B

�@���j�^�o�͗p�Ǐo���ł́A�Ǐo���J�n���Ƀf�[�^�����ݒ��łȂ�vram�̈��I�����ēǏo�����s���B���j�^�p�Ǐo�������̕��������݂��

�@�Z���Ԃł���̂ŁA�������݂�ǂ��z���ēǏo�������邱�Ƃ��Ȃ��Ȃ�A�摜�̃Y����h�~�ł���B

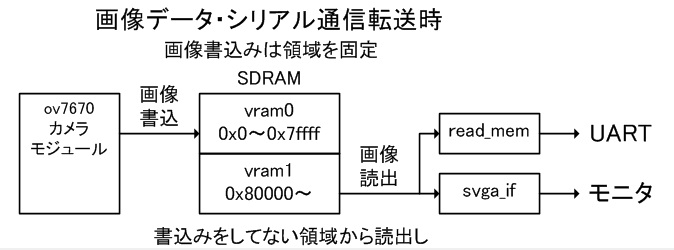

�@�@�@�V���A���ʐM�ɂ��摜�]�����s���Ă����Ԃł́A�V���A���ʐM�p�f�[�^�Ǐo���́A���j�^�o�͗p�Ǐo�����s���Ă���vram�̈悩��Ǐo�����s���B

�@�V���A���ʐM�p�f�[�^�Ǐo�������́A�摜�̏����ݎ�����蒷���̂ŁA�V���A���ʐM�p�f�[�^�Ǐo�����̉摜�f�[�^�����݂́A�Ǐo���Ɏg���ĂȂ�vram�̈�ɌŒ肷��B

�@l����ɂ��V���A���ʐM�œ]������摜�̃Y����h�~����B���̂Ƃ����j�^�o�͗p�Ǐo���̗̈���Œ肳���̂ŁA�]�����̃��j�^�\���͓]�����̉摜�̐Î~��ɂȂ�B

�@![]() �摜�]���@�\

�摜�]���@�\

�@�@'M'+CR+LF���V���A���ʐM�Ŏ�M����ƁA�摜�������ݒ��łȂ�VRAM�̈悩��f�[�^��Ǐo���ăV���A���ʐM�œ]�����܂��B

�@�V���A���ʐM�̓{�[���[�g=921.6kHz�A�f�[�^8bit�A�p���e�Bbit=�Ȃ��A�X�g�b�vbit=1bit�œ��삵�܂��B

�@�ȉ��̐}��RGB�f�[�^�̃f�[�^�t�H�[�}�b�g�ɂȂ�܂��B

�@

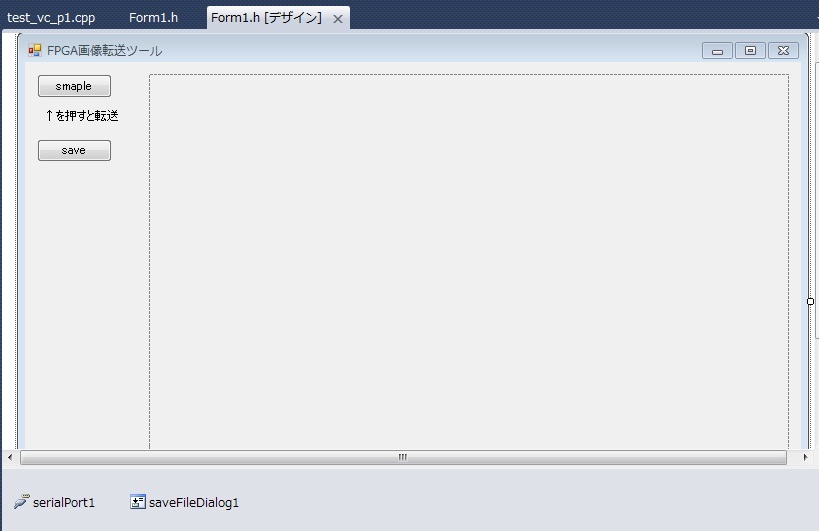

![]() PC�̉摜��荞�݃\�t�g

PC�̉摜��荞�݃\�t�g

�@�@�摜��荞�݃\�t�g�́A�����ŗ��p�ł���Microsoft Visual C++2010 Express�i�ȉ�VC++�j�ō��܂����B�T���v���f�[�^�ɓ����Ă���v���O�����́AVC++�̃����^�C�����C�u���������g�p����̂�

�@���s�ɂ�VC++�̃C���X�g�[�����K�v�ł��B�@VC++�̏ڍׂ�C���X�g�[�����@�ɂ��܂��Ă̓}�C�N���\�t�g�Ђ̃T�C�g��Q�l�������Q�l���������B

�@�܂��A�T���v���̃v���O�����͊e��ݒ��G���[�����Ȃǐ��荞��ł��܂���B�����܂ł��Q�l�p�Ƃ��l�����������B

�@�@���̐}��VC++��Form�̃f�U�C���ł��Bsample�{�^���������ƁA�V���A���ʐM��'M'+CR+LF�𑗐M���܂��B���̌��FPGA���瑗���Ă���f�[�^����M����荞��pictureBox1�ɉ摜��\�����܂��B

�@save�{�^���������ƁA�摜�f�[�^���t�@�C���ɕۑ����܂��B�R���|�[�l���g�g���C�ɂ́A�V���A���ʐM�p�R���|�[�l���g�Ƃ���serialPort1�A�t�@�C���Z�[�u�p�R���|�[�l���g�Ƃ���saveFileDialog1��z�u���Ă��܂��B

�ȉ��̓\�[�X�t�@�C���̔����itest_vc_p1_src.txt�j�ł��BVC++�̃v���O���������ۂɎQ�l�ɂ��Ă��������B

�V���A���|�[�g�̐ݒ�̓\�[�X���Ŏw�肵�Ă��܂��BCOM�|�[�g�ԍ���PC�ɂ��Ⴄ�̂Ŏg�p����PC�ɍ��킹�ĕύX�̕K�v������܂��B

�\�[�X�R�[�h��ύX���čăr���h���Ă��������B

//---------------------------------------------------------------- |

�@![]() ����̗l�q

����̗l�q

�@�@FPGA�{�[�h�ƃJ�������W���[���AFPGA�{�[�h�̉�H�_�E�����[�h�pUSB�[�q��PC��USB�[�q�AUSB-UART�ϊ���o�R��FPGA�̃V���A���ʐM�[�q��PC��USB�[�q�����ꂼ��ڑ����܂��B

�@�d��������FPGA�։�H�f�[�^���_�E�����[�h����ƃf�B�X�v���C�̒�����FPGA�̃J�����̉摜���\������܂��B����PC���̉摜��荞�݃\�t�g��sample�{�^���������ƁA

�@�V���A���ʐM��FPGA����PC�։摜���̓]�����s���܂��B�]�����̓��j�^�̉摜�͒�~���܂��B�]���ɂ�11�b������܂��B

�@�]�������������PC�̉摜��荞�݃v���O�����̃E�B���h�ɉ摜���\������܂��B

�Љ����H�������ꍇ�́A���ȐӔC�ł��肢���܂��B

�����N�t���[�ł��B![]()

�����N���ꂽ�ꍇ�͂��A��������������Ɗ������ł��B

���[���F![]()

�ύX����

(2012/8/22)�@����